45nm远不是极限!神秘的处理器制程工艺

出水蛟龙——沉浸式光刻

沉浸式光刻是AMD在45nm Phenom Ⅱ处理器生产中新应用的技术之一,其区别于过去干式光刻大的特点就是整个光刻的过程并不是发生在空气中,而是沉浸在一种光学折射率较大的透明液体中。

如果按照常识去思考,也许我们只要提高掩模板的分辨率,不就能在硅片上“刻画”出更多的MOS管来吗?从宏观上讲这是完全正确的,但不要忘了在微观的半导体制造工艺中,情况会有极大的不同。

你知道什么是光刻吗?

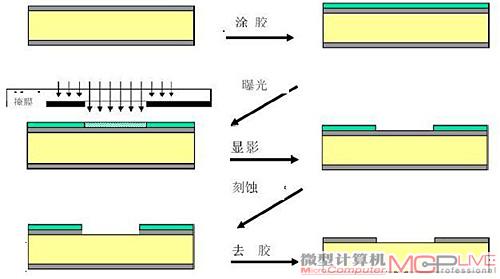

光刻技术是在一片平整的硅片上构建半导体MOS管和电路的基础,这其中包含有很多步骤与流程。首先要在硅片上涂上一层耐腐蚀的光刻胶,随后让强光通过一块刻有电路图案的镂空掩模板照射在硅片上。被照射到的部分(如源区和漏区)光刻胶会发生变质,而构筑栅区的地方不会被照射到,所以光刻胶会仍旧粘连在上面。

光刻的过程

接下来就是用腐蚀性液体清洗硅片,变质的光刻胶被除去,露出下面的硅片,而栅区在光刻胶的保护下不会受到影响。随后就是粒子沉积、掩膜、刻线等操作,直到后形成成品晶片。

如果受到保护的栅区的光刻胶留下来的宽度是130nm,那么终做出来的MOS管大致就是130nm;同理,45nm技术就是初栅极上留下大约45nm宽度的光刻胶。由此可见,如果整套光刻设备的分辨率越高,它能够在晶片上定位出更细微的投影,终就能制造出更小的MOS管。半导体工艺的更新必然伴随着光刻设备的升级,其目的就是提高分辨率。

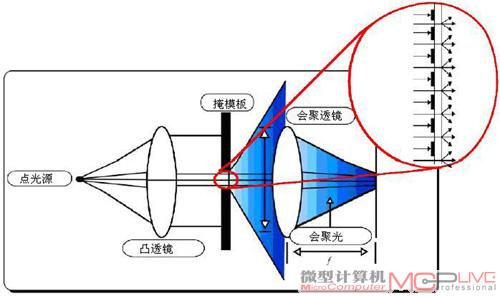

掩模板的缝隙以及投射在晶片上的阴影已经很小,这就会引发光波自身的衍射和干涉现象,导致明暗的界限不再那么分明。这样一来,就不能完成前面提到的源区、漏区以及栅区的区分标定工作,终MOS管的尺寸和性能无法达到设计要求。如果这种模糊现象进一步加剧,就会使得源区与漏区的光影基本重叠在一起,栅区无法制造,整个晶圆也就彻底报废了。

晶圆曝光过程中会因为光的衍射问题而报废

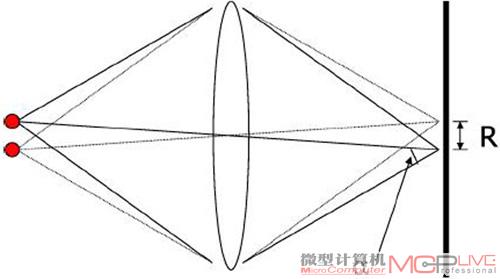

因此,大限度消除阴影就成了提高光刻分辨率的重中之重。根据光的传播汇聚理论,有一个光学中计算小分辨率的公式:R=k1λ/nθ(瑞利判据)。R代表可分辨的小尺寸(对于光刻技术来说,自然越小越好),k1是工艺常数,λ是光波波长,n为光的折射率(空气中光折射率为1),θ为两点夹角。在这个公式中,k1不可变,θ夹角也没有大幅提高的可能。因此提高分辨率,减小R的首选工作就是降低光源的光波长λ。

瑞利判据

在业界,250nm工艺及其以前的光刻工艺中采用水银灯(波长365nm)作为光源。为了提高光刻的分辨率,从180nm工艺开始采用波长为248nm的KrF(氟化氪)激光作为曝光光源;而从130nm到目前正在使用波长为193nm的ArF(氟化氩)激光作为曝光光源。但是到了45nm工艺时,193nm的ArF激光也遇到了分辨率不够的问题。同时受光刻其它配套设备的限制,取代ArF激光的新工艺还无法投入使用。因此必须寻找新的降低小分辨率的工艺。于是工程师们开始考虑改善提高光刻系统中的折射率n,这就是沉浸式光刻的理论出发点。

新型的沉浸式光刻机,可以明显看到液体循环通道

在AMD的45nm Phenom II的生产中,整个晶圆是浸泡在去离子水(无杂质,无带电离子)中的,这种情况下n=1.44,相当于将光刻的分辨率提高了1.44倍,正好满足65/45=1.44的工艺改进幅度。更好的消息是在实验室里,通过改进液体组成、光刻胶成分、镜头质量等等方法,沉浸式光刻已经能够实现22nm半导体工艺。这也意味着在未来5年内,半导体制造业还将稳定地继续发展下去。